# Section 27. USB On-The-Go (OTG)

# HIGHLIGHTS

This section of the manual contains the following major topics:

| 27.1 Introduction                              | 7-2  |

|------------------------------------------------|------|

| 27.2 Control Registers                         | 7-4  |

| 27.3 Operation                                 | 7-25 |

| 27.4 Device Mode Operation                     | 7-44 |

| 27.5 Host Mode Operation                       | 7-45 |

| 27.6 Interrupts                                | 7-51 |

| 27.7 I/O Pins                                  | 7-53 |

| 27.8 Operation in Debug and Power-Saving Modes | 7-54 |

| 27.9 Effects of a Reset                        | 7-56 |

| 27.10 Electrical Specifications                | 7-57 |

| 27.11 Register Map                             | 7-58 |

| 27.12 Related Application Notes                |      |

| 27.13 Revision History                         | 7-61 |

# 27.1 INTRODUCTION

The PIC24F USB module includes the following features:

- USB Full-Speed Support for Host and Device

- Low-Speed Host Support

- USB On-The-Go Support

- Integrated Signaling Resistors

- Integrated Analog Comparators for VBUS Monitoring

- · Integrated USB Transceiver

- · Hardware Performs Transaction Handshaking

- · Integrated DMA Controller to Access System RAM

The Universal Serial Bus (USB) module contains the analog and digital components to provide a USB 2.0 full-speed and low-speed embedded host, full-speed device or On-The-Go (OTG) implementation with a minimum of external components.

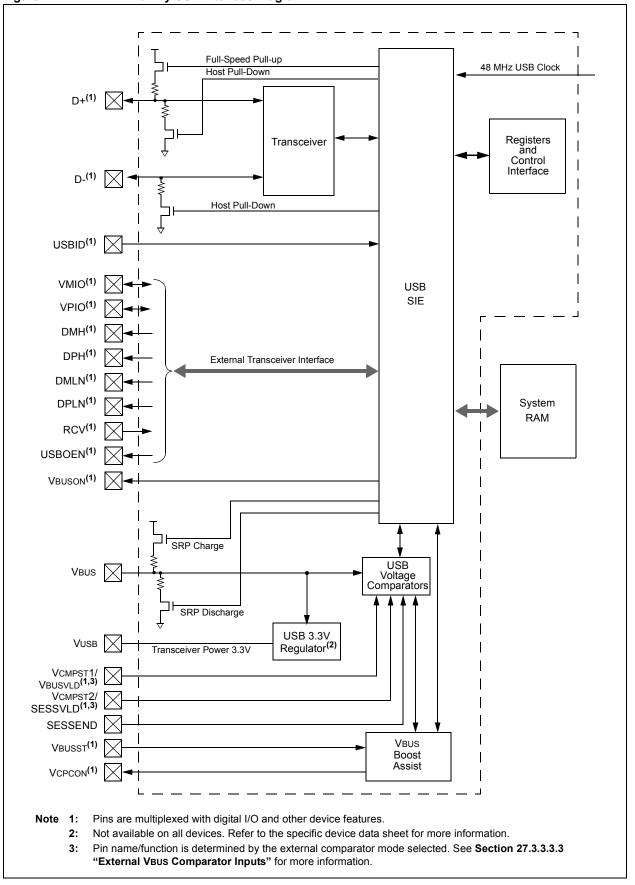

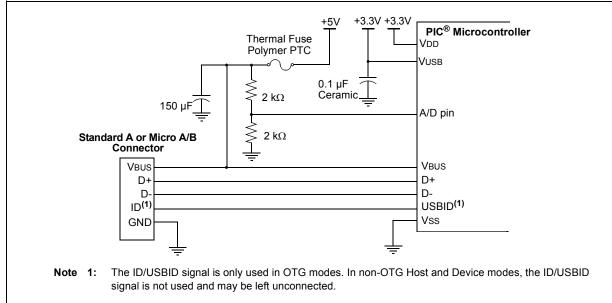

The USB module consists of the clock generator, the USB voltage comparators, the transceiver, the Serial Interface Engine (SIE), pull-up and pull-down resistors, and the register interface. Figure 27-1 shows the block diagram of the PIC24F USB OTG module.

The clock generator provides the 48 MHz clock required for USB communication. The voltage comparators monitor the voltage on the VBUS pin to determine the state of the bus. The transceiver provides the analog translation between the USB bus and the digital logic. The SIE is a state machine that transfers data to and from the endpoint buffers and generates the protocol for data transfers. The integrated pull-up and pull-down resistors eliminate the need for external signaling components. The register interface allows the CPU to configure and communicate with the module.

The dedicated USB DMA controller allows the USB module to perform direct read and write of USB packet data to the system RAM. This architecture allows the USB module to achieve effective high USB bandwidth with a minimum of microcontroller firmware processing. The dedicated USB DMA controller uses 16-bit address pointers, allowing the USB module to read or write to the first 62 kB of implemented system RAM on the microcontroller. On devices with less than 62 kB of RAM, all of the system RAM can be accessed by the USB DMA controller.

Figure 27-1: PIC24F Family USB Interface Diagram

2

On-The-Go (OTG)

# 27.2 CONTROL REGISTERS

The USB module includes the following control and status registers:

• U1OTGIR Register

The U1OTGIR register records changes of the ID and VBUS pins to enable software to determine the event causing an interrupt. The interrupt bits are cleared by writing a '1' to the respective interrupt.

U1OTGIE Register

The U1OTGIE register enables the corresponding interrupt status bits defined in the U1OTGIR register.

• U1OTGSTAT Register

The U1OTGSTAT register provides access to the status of the VBUS voltage comparators and the debounced status of the ID pin.

U1OTGCON Register

The U1OTGCON register controls the operation of the VBUS pin and the pull-up and pull-down resistors.

U1PWRC Register

The U1PWRC register controls the power-saving modes.

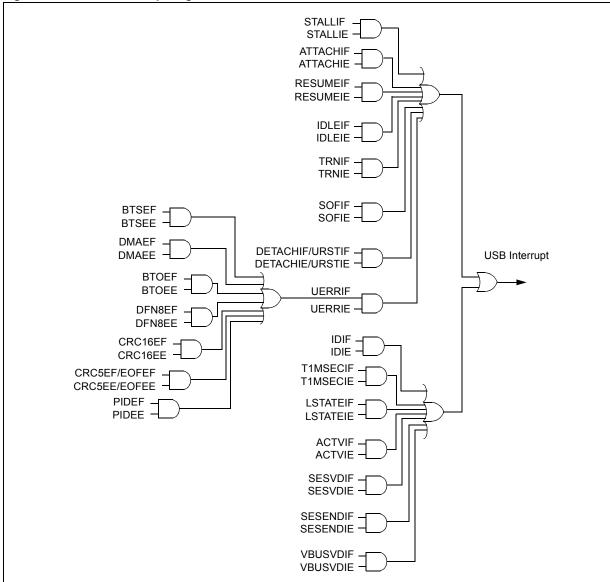

• U1IR Register

The U1IR register contains information on pending interrupts. Once an interrupt bit is set, it can be cleared by writing a '1' to the corresponding bit.

U1IE Register

The U1IE register values provide gating of the various interrupt signals onto the USB interrupt signal. These values do not interact with the USB module. Setting any of these bits enables the respective interrupt source in the U1IR register.

U1EIR Register

The U1EIR register contains information on pending error interrupt values. Once an interrupt bit is set, it can be cleared by writing a '1' to the corresponding bit.

• U1EIE Register

The U1EIE register values provide gating of the various interrupt signals onto the USB interrupt signal. These values do not interact with the USB module. Setting any of these bits enables the respective interrupt source in the U1EIR register.

• U1STAT Register

The U1STAT register is a 16-deep FIFO. It is read-only by the CPU and read/write by the USB module. U1STAT is only valid when the U1IR<TRNIF> bit is set.

U1CON Register

The U1CON register provides various control information for the module.

U1ADDR Register

The U1ADDR register is read/write from the CPU side and read-only from the USB module side. Although the register values affect the settings of the USB module, the content of the registers does not change during access.

In Device mode, this address defines the USB device address as assigned by the host during the SETUP phase. The firmware writes the address in response to the SETUP request. The address is automatically reset when a USB bus Reset is detected. In Host mode, the module transmits the address provided in this register with the corresponding token packet. This allows the USB module to uniquely address the connected device.

• U1FRMH and U1FRML Registers

The U1FRMH/U1FRML are read-only registers. The frame number is formed by concatenating the two 8-bit registers. The low-order byte is in the U1FRML register and the high-order byte is in the U1FRMH register.

U1TOK Register

The U1TOK is a read/write register required when the module operates as a host. It is used to specify the token type, PID<3:0>, and the endpoint, EP<3:0>, being addressed by the host processor. Writing to this register triggers a host transaction.

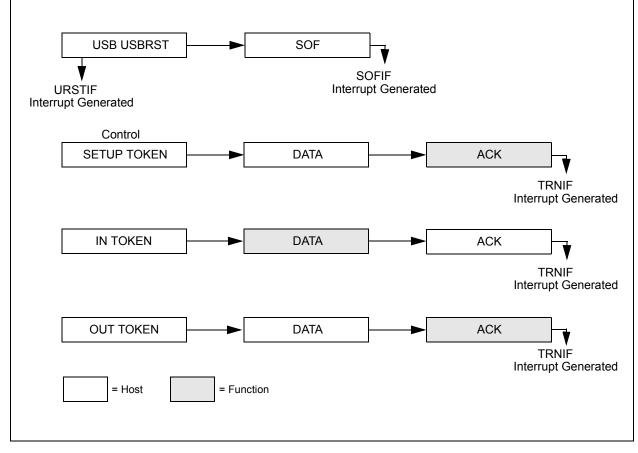

U1SOF Register

The U1SOF threshold is a read/write register that contains the count bits of the Start-of-Frame (SOF) threshold value used in Host mode only.

To prevent colliding a packet data with the Start-of-Frame (SOF) token that is sent every 1 ms, the USB module will not send any new transactions within the last U1SOF bit times. The USB module will complete any transactions that are in progress. The SOF interrupt occurs when this threshold is reached, not when the SOF occurs. Transactions started within the SOF threshold are held by the USB module until after the SOF token is sent.

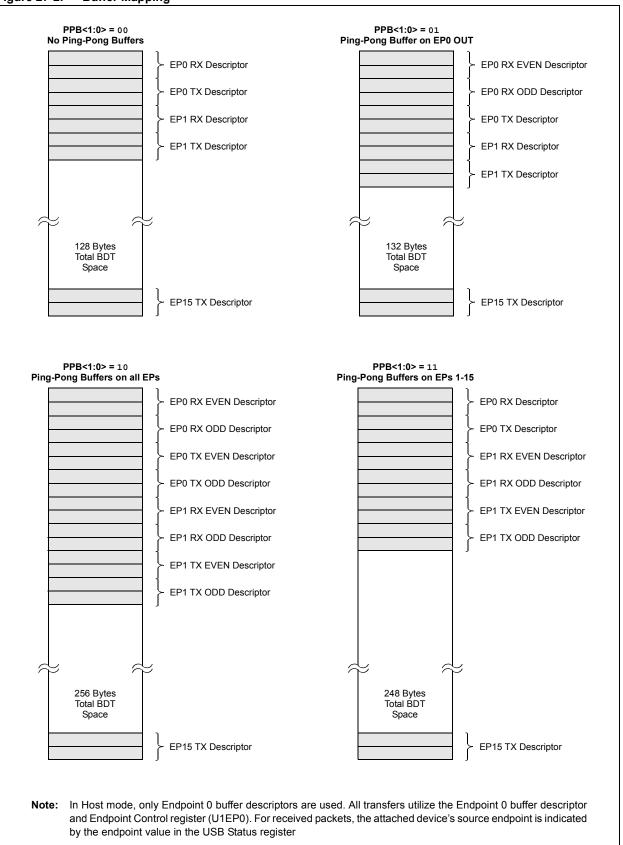

U1BDTP1

The U1BDTP1 register is a read/write register that defines the upper 7 bits of the 16-bit base address of the Buffer Descriptor Table (BDT) in the system memory. The BDT is forced to be 512 byte-aligned. This register allows real-time relocation of the BDT.

• U1CNFG1 Register

The U1CNFG1 register is a read/write register that controls the debug and Idle behavior of the module. The register must be preprogrammed prior to enabling the module.

U1CNFG2 Register

The U1CNFG2 register is a read/write register that configures interface signals.

Endpoint Control Registers

The Endpoint Control registers control the behavior of the corresponding endpoint.

The following registers are not part of the USB module but are associated with module operation.

- OSCCON: Oscillator Control Register

- IFS1: Interrupt Flag Status Registers

- IEC1: Interrupt Enable Control Registers

- DEVCFG2: Device Configuration Control Register

# 27.2.1 Clearing USB OTG Interrupts

Unlike device level interrupts, the USB OTG interrupt status flags are not freely writable in software. All USB OTG flag bits are implemented as hardware set only bits. Additionally, these bits can only be cleared in software by writing a '1' to their locations. Writing a '0' to a flag bit (i.e., a BCLR instruction) has no effect.

Issuing a "Bit Set" instruction on one of the interrupt registers is not recommended as the instruction performs a read-modify-write. The result is any interrupt flag that is already set in the register will automatically clear itself, in addition to the bit being set by the instruction. The recommended method is to write the entire register with an appropriate bit mask (Example 27-1).

**Note:** Throughout this section, a bit that can only be cleared by writing a '1' to its location is referred to as "Write '1' to clear bit". In register descriptions, this function is indicated by the descriptor, "K".

#### Example 27-1: Clearing an OTG Interrupt Flag

|                        | <pre>// write 1 to bit 0 of UlIR only,</pre>     |

|------------------------|--------------------------------------------------|

|                        | // `0' to all other bits                         |

| Ulir = $0 \times 0001$ | <pre>// clears only UlIR&lt;0&gt; (URSTIF)</pre> |

# 27.2.2 USB OTG Module Control Registers

|              |                         |                                       |                 |                   |                |                 | 1                 |

|--------------|-------------------------|---------------------------------------|-----------------|-------------------|----------------|-----------------|-------------------|

| U-0          | U-0                     | U-0                                   | U-0             | U-0               | U-0            | U-0             | U-0               |

| —            |                         | —                                     | —               | —                 | —              | —               | —                 |

| bit 15       |                         |                                       |                 |                   |                |                 | bit 8             |

|              |                         |                                       |                 |                   |                |                 |                   |

| R-0, HSC     | U-0                     | R-0, HSC                              | U-0             | R-0, HSC          | R-0, HSC       | U-0             | R-0, HSC          |

| ID           | _                       | LSTATE                                | —               | SESVD             | SESEND         |                 | VBUSVD            |

| bit 7        |                         |                                       |                 |                   |                |                 | bit 0             |

|              |                         |                                       |                 |                   |                |                 |                   |

| Legend:      |                         | U = Unimpleme                         | ented bit, read | d as '0'          |                |                 |                   |

| R = Readab   | le bit                  | W = Writable b                        | it              | HSC = Hardw       | are Settable/C | earable bit     |                   |

| -n = Value a | t POR                   | '1' = Bit is set                      |                 | '0' = Bit is clea | ared           | x = Bit is unk  | nown              |

|              |                         |                                       |                 |                   |                |                 |                   |

| bit 15-8     | Unimplemen              | ted: Read as '0'                      |                 |                   |                |                 |                   |

| bit 7        | ID: ID Pin Sta          | te Indicator bit                      |                 |                   |                |                 |                   |

|              |                         | is attached or a                      |                 |                   |                | 3 receptacle    |                   |

| 1.11.0       |                         | plug has been p                       |                 | ie USB recepta    | cie            |                 |                   |

| bit 6        | •                       | ted: Read as '0'                      |                 |                   |                |                 |                   |

| bit 5        |                         | e State Stable Ind                    |                 |                   |                | <b>6</b>        |                   |

|              |                         | line state (as de<br>line state has N |                 |                   |                | e for the previ | ous 1 ms          |

| bit 4        | Unimplemen              | ted: Read as '0'                      |                 |                   |                |                 |                   |

| bit 3        | SESVD: Sess             | sion Valid Indicat                    | tor bit         |                   |                |                 |                   |

|              | 1 = The VBU<br>B-device | s voltage is abov                     | ve VA_SESS_\    | /LD (as defined   | in the USB OT  | G Specificati   | on) on the A or   |

|              | 0 = The VBUS            | s voltage is belov                    | w VA_SESS_V     | LD on the A or E  | 3-device       |                 |                   |

| bit 2        | SESEND: B-S             | Session End Indi                      | icator bit      |                   |                |                 |                   |

|              | 1 = The VBU<br>B-device | s voltage is bel                      | low VB_SESS     | _END (as define   | ed in the USE  | OTG Specif      | ication) on the   |

|              | 0 = The VBUS            | s voltage is abov                     | e VB_SESS_E     | ND on the B-de    | vice           |                 |                   |

| bit 1        | Unimplemen              | ted: Read as '0'                      | 1               |                   |                |                 |                   |

| bit 0        | VBUSVD: A-              | VBUS Valid Indica                     | ator bit        |                   |                |                 |                   |

|              | 1 = The VBU             | e voltago is ab                       | OVA VA VRUS     | VID (as defin     | ed in the USE  | OTG Specif      | insticus) and the |

|              | A-device                |                                       |                 |                   |                |                 | ication) on the   |

# Register 27-1: U1OTGSTAT: USB OTG Status Register

| U-0          | U-0           | U-0                                    | U-0                       | U-0                   | U-0                  | U-0                    | U-0                    |

|--------------|---------------|----------------------------------------|---------------------------|-----------------------|----------------------|------------------------|------------------------|

|              |               |                                        |                           |                       |                      |                        |                        |

| oit 15       |               |                                        |                           |                       |                      |                        | bit 8                  |

|              |               |                                        |                           |                       |                      |                        |                        |

| R/W-0        | R/W-0         | R/W-0                                  | R/W-0                     | R/W-0                 | R/W-0                | R/W-0                  | R/W-0                  |

| DPPULUF      | P DMPULUP     | DPPULDWN <sup>(1)</sup>                | DMPULDWN <sup>(1)</sup>   | VBUSON <sup>(1)</sup> | OTGEN <sup>(1)</sup> | VBUSCHG <sup>(1)</sup> | VBUSDIS <sup>(1)</sup> |

| bit 7        |               |                                        |                           |                       |                      |                        | bit (                  |

| Legend:      |               |                                        |                           |                       |                      |                        |                        |

| R = Readat   | ole bit       | W = Writable                           | bit                       | U = Unimplem          | ented bit rea        | d as '0'               |                        |

| -n = Value a |               | '1' = Bit is set                       |                           | '0' = Bit is clea     |                      | x = Bit is unkr        | nown                   |

|              |               |                                        |                           |                       |                      |                        |                        |

| bit 15-8     | Unimplemen    | ted: Read as 'd                        | )'                        |                       |                      |                        |                        |

| oit 7        | DPPULUP: D    | )+ Pull-Up Enat                        | ole bit                   |                       |                      |                        |                        |

|              | 1 = D+ data l | line pull-up resis                     | stor is enabled           |                       |                      |                        |                        |

|              | 0 = D+ data l | line pull-up resis                     | stor is disabled          | 1                     |                      |                        |                        |

| bit 6        |               | D- Pull-Up Enab                        |                           |                       |                      |                        |                        |

|              |               | ine pull-up resis                      |                           |                       |                      |                        |                        |

|              |               | ine pull-up resis                      |                           |                       |                      |                        |                        |

| bit 5        | -             | : D+ Pull-Down                         |                           |                       |                      |                        |                        |

|              |               | line pull-down re<br>line pull-down re |                           |                       |                      |                        |                        |

| bit 4        |               | : D- Pull-Down                         |                           | icu -                 |                      |                        |                        |

|              |               | ine pull-down re                       |                           | ed                    |                      |                        |                        |

|              |               | ine pull-down re                       |                           |                       |                      |                        |                        |

| bit 3        | VBUSON: VE    | sus Power-on b                         | it <sup>(1)</sup>         |                       |                      |                        |                        |

|              | 1 = VBUS line | e is powered                           |                           |                       |                      |                        |                        |

|              |               | e is not powered                       |                           |                       |                      |                        |                        |

| bit 2        | OTGEN: OTO    | G Features Ena                         | ble bit <sup>(1)</sup>    |                       |                      |                        |                        |

|              |               |                                        |                           |                       |                      | the DPPULxxx/[         |                        |

|              |               | G disabled; D+/<br>TEN and USBE        |                           |                       | re controlled i      | n hardware by          | the settings c         |

| bit 1        |               | /BUS Charge Se                         | •                         | 1 0,0 7               |                      |                        |                        |

|              |               | e set to charge t                      |                           |                       |                      |                        |                        |

|              | 0 = VBUS line | e set to charge t                      | to 5V                     |                       |                      |                        |                        |

| bit 0        | VBUSDIS: VE   | BUS Discharge I                        | Enable bit <sup>(1)</sup> |                       |                      |                        |                        |

|              | 1 = VBUS line | e discharged thr                       | ough a resisto            | r                     |                      |                        |                        |

|              |               | e not discharged                       |                           |                       |                      |                        |                        |

Note 1: These bits are only used in Host mode; do not use in Device mode.

27

USB On-The-Go (OTG)

| 11.0          | 11.0                  | 11.0                      |                     | 11.0                                    | 11.0           | 11.0           | 11.0           |  |

|---------------|-----------------------|---------------------------|---------------------|-----------------------------------------|----------------|----------------|----------------|--|

| U-0           | U-0                   | U-0                       | U-0                 | U-0                                     | U-0            | U-0            | U-0            |  |

| —             | —                     | —                         |                     | —                                       | —              | —              | —              |  |

| bit 15        |                       |                           |                     |                                         |                |                | bit 8          |  |

|               |                       |                           |                     |                                         |                |                |                |  |

| R-x, HSC      | U-0                   | U-0                       | R/W                 | U-0                                     | U-0            | R/W-0, HC      | R/W-0          |  |

| UACTPND       | —                     | —                         | USLPGRD             |                                         | _              | USUSPND        | USBPWR         |  |

| bit 7         |                       | ·                         | •                   |                                         |                |                | bit 0          |  |

|               |                       |                           |                     |                                         |                |                |                |  |

| Legend:       |                       | HC = Hardware             | e Clearable bit     | HSC = Hardv                             | vare Settable/ | Clearable bit  |                |  |

| R = Readabl   | le bit                | W = Writable b            | it                  | U = Unimplemented bit, read as '0'      |                |                |                |  |

| -n = Value at | t POR                 | '1' = Bit is set          |                     | '0' = Bit is cleared x = Bit is unknown |                |                |                |  |

|               |                       |                           |                     |                                         |                |                |                |  |

| bit 15-8      | Unimpleme             | nted: Read as '0          | ,                   |                                         |                |                |                |  |

| bit 7         | UACTPND:              | USB Activity Per          | nding bit           |                                         |                |                |                |  |

|               | 1 = Module s          | should not be su          | spended at the r    | moment (requir                          | es GUARD b     | it to be set)  |                |  |

|               | 0 = Module r          | may be suspende           | ed or powered d     | lown                                    |                |                |                |  |

| bit 6-5       | Unimpleme             | nted: Read as '0          | 3                   |                                         |                |                |                |  |

| bit 4         | USLPGRD:              | Sleep Guard bit           |                     |                                         |                |                |                |  |

|               | 1 = Indicate          | to the USB modu           | ule that it is abou | ut to be susper                         | nded or power  | red down       |                |  |

|               | 0 = No susp           | end                       |                     |                                         |                |                |                |  |

| bit 3-2       | Unimpleme             | nted: Read as '0          | ,                   |                                         |                |                |                |  |

| bit 1         | USUSPND:              | USB Suspend M             | ode Enable bit      |                                         |                |                |                |  |

|               | 1 = USB OT<br>low-pow | rG module is in ver state | Suspend mode        | ; USB clock is                          | s gated and t  | he transceiver | is placed in a |  |

# Register 27-3: U1PWRC: USB Power Control Register

- bit 0 USBPWR: USB Operation Enable bit

- 1 = USB OTG module is enabled

0 = Normal USB OTG operation

- 0 = USB OTG module is disabled<sup>(1)</sup>

- **Note 1:** Do not clear this bit unless the HOSTEN, USBEN and OTGEN bits (U1CON<3,0> and U1OTGCON<2>) are all cleared.

| Register 27-4:        | U1STAT                | : USB Status I                                        | Register                                                    |                   |                             |                 |       |

|-----------------------|-----------------------|-------------------------------------------------------|-------------------------------------------------------------|-------------------|-----------------------------|-----------------|-------|

| U-0                   | U-0                   | U-0                                                   | U-0                                                         | U-0               | U-0                         | U-0             | U-0   |

| _                     |                       | —                                                     | —                                                           | —                 | —                           | _               | —     |

| bit 15                |                       |                                                       |                                                             |                   |                             |                 | bit 8 |

| R-0, HSC              | R-0, HSC              | R-0, HSC                                              | R-0, HSC                                                    | R-0, HSC          | R-0, HSC                    | U-0             | U-0   |

| ENDPT3 <sup>(2)</sup> | ENDPT2 <sup>(2)</sup> | ENDPT1 <sup>(2)</sup>                                 | ENDPT0 <sup>(2)</sup>                                       | DIR               | PPBI <sup>(1)</sup>         | 0-0             | 0-0   |

| bit 7                 | ENDF12"               | ENDETRY                                               | ENDETO: /                                                   | DIK               | FFDN /                      |                 | bit 0 |

|                       |                       |                                                       |                                                             |                   |                             |                 | DILU  |

| Legend:               |                       | U = Unimplen                                          | nented bit, read                                            | 1 as '0'          |                             |                 |       |

| R = Readable          | bit                   | W = Writable                                          | bit                                                         | HSC = Hardw       | are Settable/C              | learable bit    |       |

| -n = Value at F       | POR                   | '1' = Bit is set                                      |                                                             | '0' = Bit is clea | ared                        | x = Bit is unki | nown  |

|                       |                       | point 15<br>point 14<br>point 1                       |                                                             | d by the last US  | SB transfer) <sup>(2)</sup> |                 |       |

| bit 3                 | 1 = The last t        | Direction Indic<br>transaction was<br>transaction was | a transmit tra                                              |                   |                             |                 |       |

| bit 2                 | PPBI: Ping-P          | ong BD Pointe<br>transaction was                      | <sup>r</sup> Indicator bit <sup>(1)</sup><br>s to the ODD B | D bank            |                             |                 |       |

|                       | 0 = The last t        | transaction was                                       |                                                             |                   |                             |                 |       |

2: In Host mode, all transactions are processed through Endpoint 0 and the Endpoint 0 BDTs; therefore, ENDPT<3:0> will always read as '0000'.

27

USB On-The-Go (OTG)

# PIC24F Family Reference Manual

| U-0            | U-0                                                                                                                                                                        | U-0                                                                                                                                                                                                                | U-0                                                                                                                     | U-0               | U-0                                   | U-0              | U-0           |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|-------------------|---------------------------------------|------------------|---------------|

|                |                                                                                                                                                                            |                                                                                                                                                                                                                    | _                                                                                                                       | _                 |                                       |                  | _             |

| bit 15         |                                                                                                                                                                            |                                                                                                                                                                                                                    |                                                                                                                         |                   |                                       |                  | bit 8         |

|                |                                                                                                                                                                            |                                                                                                                                                                                                                    |                                                                                                                         |                   |                                       |                  |               |

| U-0            | R-x HSC                                                                                                                                                                    | R/W-0                                                                                                                                                                                                              | U-0                                                                                                                     | R/W-0             | R/W-0                                 | R/W-0            | R/W-0         |

|                | SE0                                                                                                                                                                        | PKTDIS                                                                                                                                                                                                             | _                                                                                                                       | HOSTEN            | RESUME                                | PPBRST           | USBEN         |

| bit 7          |                                                                                                                                                                            |                                                                                                                                                                                                                    |                                                                                                                         |                   |                                       |                  | bit (         |

| Logondi        |                                                                                                                                                                            |                                                                                                                                                                                                                    | optod bit roa                                                                                                           |                   |                                       |                  |               |

| Legend:        | -1- h:4                                                                                                                                                                    | U = Unimplem                                                                                                                                                                                                       |                                                                                                                         |                   |                                       | la analula kit   |               |

| R = Readal     |                                                                                                                                                                            | W = Writable I                                                                                                                                                                                                     | DIT                                                                                                                     | HSC = Hardwa      |                                       |                  |               |

| -n = Value a   | at POR                                                                                                                                                                     | '1' = Bit is set                                                                                                                                                                                                   |                                                                                                                         | '0' = Bit is clea | ired                                  | x = Bit is unkn  | own           |

| bit 15-7       | Unimplomor                                                                                                                                                                 | nted: Read as '0                                                                                                                                                                                                   | , ,                                                                                                                     |                   |                                       |                  |               |

| bit 6          | -                                                                                                                                                                          | ngle-Ended Zero                                                                                                                                                                                                    |                                                                                                                         |                   |                                       |                  |               |

|                |                                                                                                                                                                            | nded zero active                                                                                                                                                                                                   | •                                                                                                                       | bue               |                                       |                  |               |

|                | •                                                                                                                                                                          | e-ended zero de                                                                                                                                                                                                    |                                                                                                                         | 503               |                                       |                  |               |

| bit 5          | PKTDIS: Pad                                                                                                                                                                | cket Transfer Dis                                                                                                                                                                                                  | sable bit                                                                                                               |                   |                                       |                  |               |

|                | 1 = SIE toke                                                                                                                                                               | n and packet pr                                                                                                                                                                                                    | ocessing disa                                                                                                           | bled; automatica  | ally set when a                       | SETUP token      | is received   |

|                | 0 = SIE toke                                                                                                                                                               | n and packet pr                                                                                                                                                                                                    | ocessing ena                                                                                                            | bled              |                                       |                  |               |

| bit 4          | -                                                                                                                                                                          | nted: Read as '0                                                                                                                                                                                                   |                                                                                                                         |                   |                                       |                  |               |

| bit 3          |                                                                                                                                                                            | ost Mode Enable                                                                                                                                                                                                    |                                                                                                                         |                   |                                       |                  |               |

|                | 1 = USB mc                                                                                                                                                                 | dulo oporatos i                                                                                                                                                                                                    | n Host modo                                                                                                             | when 111DW/DC     | C<0> is set: p                        | ull-downs on D   |               |

|                |                                                                                                                                                                            | •                                                                                                                                                                                                                  |                                                                                                                         |                   | · · · · · · · · · · · · · · · · · · · |                  | + and D- are  |

|                | activated                                                                                                                                                                  | d in hardware                                                                                                                                                                                                      |                                                                                                                         |                   | · · · · · · · · · ·                   |                  | )+ and D- ar€ |

| hit 2          | activated<br>0 = USB hos                                                                                                                                                   | d in hardware<br>st capability disa                                                                                                                                                                                | bled                                                                                                                    | when on whe       |                                       |                  | )+ and D- are |

| bit 2          | activated<br>0 = USB hos<br><b>RESUME:</b> R                                                                                                                               | d in hardware<br>st capability disa<br>esume Signaling                                                                                                                                                             | bled<br>g Enable bit                                                                                                    | when on whe       |                                       |                  | )+ and D- are |

| bit 2          | activated<br>0 = USB hos<br><b>RESUME:</b> R<br>1 = Resume                                                                                                                 | d in hardware<br>st capability disa                                                                                                                                                                                | bled<br>9 Enable bit<br>ted                                                                                             | when on whe       |                                       |                  | )+ and D- are |

| bit 2<br>bit 1 | activated<br>0 = USB hos<br><b>RESUME:</b> Re<br>1 = Resume<br>0 = Resume                                                                                                  | d in hardware<br>st capability disa<br>esume Signaling<br>signaling activa<br>signaling disabl                                                                                                                     | bled<br>gEnable bit<br>ted<br>ed                                                                                        | when on whe       |                                       |                  | ו+ and D- are |

|                | activated<br>0 = USB hos<br><b>RESUME:</b> R<br>1 = Resume<br>0 = Resume<br><b>PPBRST:</b> Pir                                                                             | d in hardware<br>st capability disa<br>esume Signaling<br>signaling activa<br>signaling disabl<br>ng-Pong Buffers                                                                                                  | bled<br>9 Enable bit<br>ted<br>ed<br>Reset bit                                                                          | o the EVEN BD     |                                       |                  | ו+ and D- are |

|                | activated<br>0 = USB hos<br><b>RESUME:</b> R<br>1 = Resume<br>0 = Resume<br><b>PPBRST:</b> Pir<br>1 = Reset a                                                              | d in hardware<br>st capability disa<br>esume Signaling<br>signaling activa<br>signaling disabl<br>ng-Pong Buffers                                                                                                  | bled<br>9 Enable bit<br>ted<br>ed<br>Reset bit<br>ffer Pointers t                                                       |                   |                                       |                  | ו+ and D- are |

| bit 1          | activated<br>0 = USB hos<br><b>RESUME:</b> R<br>1 = Resume<br>0 = Resume<br><b>PPBRST:</b> Pir<br>1 = Reset a<br>0 = Ping-Po                                               | d in hardware<br>st capability disa<br>esume Signaling<br>signaling activa<br>signaling disabl<br>ng-Pong Buffers<br>Il Ping-Pong But                                                                              | bled<br>Enable bit<br>ted<br>ed<br>Reset bit<br>ffer Pointers t<br>ers not reset                                        |                   |                                       |                  | ו+ and D- are |

|                | activated<br>0 = USB hos<br><b>RESUME:</b> R<br>1 = Resume<br>0 = Resume<br><b>PPBRST:</b> Pir<br>1 = Reset a<br>0 = Ping-Po<br><b>USBEN:</b> USI<br>1 = USB mo            | d in hardware<br>st capability disa<br>esume Signaling<br>signaling activa<br>signaling disabl<br>ng-Pong Buffers<br>II Ping-Pong Buf<br>ng Buffer Pointe<br>B Device Mode I<br>odule operates                     | bled<br>g Enable bit<br>ted<br>ed<br>Reset bit<br>ffer Pointers t<br>ers not reset<br>Enable bit<br>in Device mo        |                   | banks                                 | t; D+ pull-up is |               |

| bit 1          | activated<br>0 = USB hos<br><b>RESUME:</b> R<br>1 = Resume<br>0 = Resume<br><b>PPBRST:</b> Pir<br>1 = Reset a<br>0 = Ping-Po<br><b>USBEN:</b> USB<br>1 = USB mo<br>hardwar | d in hardware<br>st capability disa<br>esume Signaling<br>signaling activa<br>signaling disabl<br>ng-Pong Buffers<br>II Ping-Pong Buf<br>ng Buffer Pointe<br>B Device Mode I<br>odule operates<br>e (device attach | bled<br>g Enable bit<br>ted<br>ed<br>Reset bit<br>ffer Pointers t<br>ers not reset<br>Enable bit<br>in Device mo<br>ed) | o the EVEN BD     | banks<br>VRC<0> is se                 | t; D+ pull-up is |               |

# **Note 1:** Some USB module register bit definitions/usages depend on the state of the HOSTEN and USBEN bits i the U1CON register. The bit definitions shown in this register description apply when HOSTEN = 0.

| U-0          | U-0                                    | U-0                                 | U-0                  | U-0                | U-0             | U-0               | U-0            |

|--------------|----------------------------------------|-------------------------------------|----------------------|--------------------|-----------------|-------------------|----------------|

| —            |                                        | _                                   |                      | —                  | _               |                   | —              |

| oit 15       |                                        |                                     |                      |                    |                 |                   | bit 8          |

|              |                                        |                                     |                      |                    |                 |                   |                |

| R-x, HSC     | R-x, HSC                               | R/W-0                               | R/W-0                | R/W-0              | R/W-0           | R/W-0             | R/W-0          |

| JSTATE       | SE0                                    | TOKBUSY                             | USBRST               | HOSTEN             | RESUME          | PPBRST            | SOFEN          |

| bit 7        |                                        |                                     |                      |                    |                 |                   | bit (          |

|              |                                        |                                     |                      |                    |                 |                   |                |

| Legend:      |                                        | U = Unimplem                        | ented bit, rea       | d as '0'           |                 |                   |                |

| R = Readabl  | le bit                                 | W = Writable                        | oit                  | HSC = Hardw        | are Settable/C  | learable bit      |                |

| n = Value at | t POR                                  | '1' = Bit is set                    |                      | '0' = Bit is clea  | ared            | x = Bit is unkr   | nown           |

|              |                                        |                                     |                      |                    |                 |                   |                |

| bit 15-8     | Unimplemen                             | ted: Read as '                      | )'                   |                    |                 |                   |                |

| bit 7        | JSTATE: Live                           | e Differential Re                   | ceiver J State       | Flag bit           |                 |                   |                |

|              | 1 = J state (d                         | ifferential '0' in                  | ow speed, diff       | erential '1' in fu | II speed) detec | ted on the USE    | 3              |

|              | 0 = No J state                         | e detected                          |                      |                    |                 |                   |                |

| bit 6        |                                        | gle-Ended Zero                      | -                    |                    |                 |                   |                |

|              | •                                      | nded zero active                    |                      | ous                |                 |                   |                |

| L:4 F        | -                                      | e-ended zero de                     |                      |                    |                 |                   |                |

| bit 5        |                                        | oken Busy Stat                      |                      | dula in On Tha     | Colotato        |                   |                |

|              |                                        | being executed b                    |                      | dule in On-The-    | Goslale         |                   |                |

| bit 4        |                                        | dule Reset bit                      |                      |                    |                 |                   |                |

|              | 1 = USB Res<br>clear it <sup>(1)</sup> | set has been ge                     | enerated; for S      | oftware Reset,     | application mu  | st set this bit f | or 50 ms, thei |

|              | 0 = USB Res                            | set terminated                      |                      |                    |                 |                   |                |

| bit 3        | HOSTEN: Ho                             | st Mode Enable                      | e bit <sup>(2)</sup> |                    |                 |                   |                |

|              |                                        |                                     | n Host mode          | when U1PWR         | C<0> is set; p  | ull-downs on [    | 0+ and D- ar   |

|              |                                        | l in hardware<br>t mode circuitry   | dischlod             |                    |                 |                   |                |

| bit 2        |                                        | -                                   |                      |                    |                 |                   |                |

|              |                                        | esume Signaling                     |                      | e must set bit f   | or 10 ms and    | then clear to a   | anahla ramoti  |

|              | wake-up                                |                                     |                      |                    |                 |                   |                |

|              | 0 = Resume                             | signaling disab                     | led                  |                    |                 |                   |                |

| bit 1        | PPBRST: Pin                            | g-Pong Buffers                      | Reset bit            |                    |                 |                   |                |

|              |                                        | ll Ping-Pong Bu<br>ng Buffer Pointe |                      | the EVEN BD        | banks           |                   |                |

| bit 0        | SOFEN: Star                            | t-of-Frame Ena                      | ble bit              |                    |                 |                   |                |

|              | 1 = Start-of-F                         | -<br>rame token au                  | tomatically ser      | nt every 1 millis  | econd           |                   |                |

|              | 0 = Start-of-F                         | Frame token ge                      | neration disab       | led                |                 |                   |                |

|              | lay be a continu<br>otal at least 50 m |                                     |                      |                    |                 |                   | st 10 ms that  |

|              |                                        |                                     |                      |                    |                 |                   |                |

2: Some USB module register bit definitions/usages depend on the state of the HOSTEN (and USBEN) bits in the U1CON register. The bit definitions shown in this register description apply when HOSTEN = 1.

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

# Register 27-7: U1ADDR: USB Address Register

| R/W-0                 | R/W-0    | R/W-0    | R/W-0    | R/W-0    | R/W-0    | R/W-0    | R/W-0    |

|-----------------------|----------|----------|----------|----------|----------|----------|----------|

| LSPDEN <sup>(1)</sup> | DEVADDR6 | DEVADDR5 | DEVADDR4 | DEVADDR3 | DEVADDR2 | DEVADDR1 | DEVADDR0 |

| bit 7                 |          |          |          |          |          |          | bit 0    |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-8 Unimplemented: Read as '0'

| bit 7 | LSPDEN: Low-Speed Enable bit <sup>(1)</sup> |

|-------|---------------------------------------------|

|       | 1 = LISB module operates at low spee        |

- 1 = USB module operates at low speed

0 = USB module operates at full speed

- 0 = 0.5B module operates at full spee

| DIT 6-0 DEVADDR<6:0>: USB Device Address Dits | bit 6-0 | DEVADDR<6:0>: USB Device Address bits |

|-----------------------------------------------|---------|---------------------------------------|

|-----------------------------------------------|---------|---------------------------------------|

Note 1: Host mode only. In Device mode, this bit is unimplemented and the module operates at full speed.

|                     | • • • • • •                       |                                     | legiotoi (meet      | line as enig,                      |        |                    |       |  |

|---------------------|-----------------------------------|-------------------------------------|---------------------|------------------------------------|--------|--------------------|-------|--|

| U-0                 | U-0                               | U-0                                 | U-0                 | U-0                                | U-0    | U-0                | U-0   |  |

|                     | _                                 |                                     | —                   | —                                  | —      | —                  | —     |  |

| bit 15              |                                   |                                     |                     |                                    |        |                    | bit 8 |  |

|                     |                                   |                                     |                     |                                    |        |                    |       |  |

| R/W-0               | R/W-0                             | R/W-0                               | R/W-0               | R/W-0                              | R/W-0  | R/W-0              | R/W-0 |  |

| PID3 <sup>(1)</sup> | PID2 <sup>(1)</sup>               | PID1 <sup>(1)</sup>                 | PID0 <sup>(1)</sup> | EP3                                | EP2    | EP1                | EP0   |  |

| bit 7               |                                   |                                     |                     |                                    |        |                    | bit 0 |  |

|                     |                                   |                                     |                     |                                    |        |                    |       |  |

| Legend:             |                                   |                                     |                     |                                    |        |                    |       |  |

| R = Readabl         | R = Readable bit W = Writable bit |                                     | bit                 | U = Unimplemented bit, read as '0' |        |                    |       |  |

| -n = Value at POR   |                                   | '1' = Bit is set                    |                     | '0' = Bit is cleared               |        | x = Bit is unknown |       |  |

| bit 15-8            | Unimplemen                        | ted: Read as '                      | o'                  |                                    |        |                    |       |  |

| bit 7-4             |                                   | ken Type Ident                      |                     |                                    |        |                    |       |  |

| Dit 7-4             | 1101 <b>= SETU</b>                | JP (TX) token t                     | ype transactior     | n                                  |        |                    |       |  |

|                     | •                                 | X) token type to<br>(TX) token type |                     |                                    |        |                    |       |  |

| bit 3-0             | EP<3:0>: Tok                      | ken Command                         | Endpoint Addr       | ess bits                           |        |                    |       |  |

|                     | This value mu                     | ust specify a va                    | lid endpoint or     | n the attached d                   | evice. |                    |       |  |

|                     |                                   |                                     |                     |                                    |        |                    |       |  |

# Register 27-8: U1TOK: USB Token Register (Host Mode Only)

Note 1: All other combinations are reserved and are not to be used.

| U-0    | U-0   | U-0   | U-0   | U-0   | U-0   | U-0   | U-0   |

|--------|-------|-------|-------|-------|-------|-------|-------|

|        | _     | —     | —     | —     | —     | —     | —     |

| bit 15 |       |       |       |       |       |       | bit 8 |

|        |       |       |       |       |       |       |       |

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

| CNT7   | CNT6  | CNT5  | CNT4  | CNT3  | CNT2  | CNT1  | CNT0  |

| bit 7  |       |       |       |       |       |       | bit 0 |

|        |       |       |       |       |       |       |       |

| Register 27-9: | U1SOF: USB OTG Start-of-Token Threshold Register (Host Mode Only) |

|----------------|-------------------------------------------------------------------|

|----------------|-------------------------------------------------------------------|

| Legend:           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 15-8 Unimplemented: Read as '0'

#### Register 27-10: U1CNFG1: USB Configuration Register 1

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | —   | _   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-0 | R/W-0  | U-0 | R/W-0   | U-0 | U-0 | R/W-0 | R/W-0 |

|-------|--------|-----|---------|-----|-----|-------|-------|

| UTEYE | UOEMON | —   | USBSIDL | —   | —   | PPB1  | PPB0  |

| bit 7 |        |     |         |     |     |       | bit 0 |

| Legend:           |                       |                       |                    |

|-------------------|-----------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit      | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set      | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-8 Unimp    | lemented: Read as '0' |                       |                    |

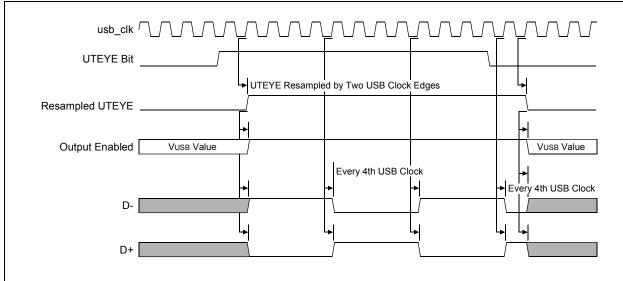

| <ul> <li>1 = Eye pattern test enabled         <ul> <li>0 = Eye pattern test disabled</li> </ul> </li> <li>6 UOEMON: USB OE Monitor Enable bit         <ul> <li>1 = OE signal active; it indicates intervals during which the D+/D- lines are driving                 0 = OE signal inactive<sup>(1)</sup></li> </ul> </li> <li>5 Unimplemented: Read as '0'         <ul> <li>4 USBSIDL: USB OTG Stop in Idle Mode bit                 1 = Discontinue module operation when device enters Idle mode</li> </ul> </li> </ul> |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>6 UOEMON: USB OE Monitor Enable bit         <ol> <li>I = OE signal active; it indicates intervals during which the D+/D- lines are driving             0 = OE signal inactive<sup>(1)</sup></li> </ol> </li> <li>5 Unimplemented: Read as '0'         <ol> <li>USBSIDL: USB OTG Stop in Idle Mode bit</li> </ol> </li> </ul>                                                                                                                                                                                      |

| <ul> <li>1 = OE signal active; it indicates intervals during which the D+/D- lines are driving</li> <li>0 = OE signal inactive<sup>(1)</sup></li> <li>Unimplemented: Read as '0'</li> <li>USBSIDL: USB OTG Stop in Idle Mode bit</li> </ul>                                                                                                                                                                                                                                                                                |

| <ul> <li>0 = OE signal inactive<sup>(1)</sup></li> <li>Unimplemented: Read as '0'</li> <li>USBSIDL: USB OTG Stop in Idle Mode bit</li> </ul>                                                                                                                                                                                                                                                                                                                                                                               |

| 4 USBSIDL: USB OTG Stop in Idle Mode bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| <ol> <li>1 = Discontinue module operation when device enters Idle mode</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| <ul><li>0 = Continue module operation in Idle mode</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 3-2 Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

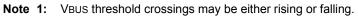

| 1-0 <b>PPB&lt;1:0&gt;:</b> Ping-Pong Buffers Configuration bits                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 11 = EVEN/ODD ping-pong buffers enabled for Endpoints 1 to 15                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| <ul><li>11 = EVEN/ODD ping-pong buffers enabled for Endpoints 1 to 15</li><li>10 = EVEN/ODD ping-pong buffers enabled for all endpoints</li></ul>                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| <ul> <li>0 = Continue module operation in Idle mode</li> <li>3-2 Unimplemented: Read as '0'</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                     |

**Note 1:** When the UTRDIS bit (U1CNFG2<0>) is set, the  $\overline{OE}$  signal is active regardless of the setting of UOEMON.

bit 7-0 **CNT<7:0:>** Start-of-Frame Count bits Value represents 10 + (packet size of n bytes); for example: 0100 1010 = 64-byte packet 0010 1010 = 32-byte packet 0001 0010 = 8-byte packet

| U-0           | U-0                                                                   | U-0                                               | U-0             | U-0                       | U-0                     | U-0                     | U-0                   |  |  |

|---------------|-----------------------------------------------------------------------|---------------------------------------------------|-----------------|---------------------------|-------------------------|-------------------------|-----------------------|--|--|

| _             | —                                                                     | —                                                 | _               | —                         | —                       | —                       | —                     |  |  |

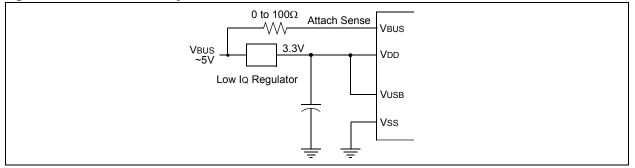

| bit 15        |                                                                       |                                                   |                 |                           |                         |                         | bit 8                 |  |  |